KSZ8863RLL tres puertos 10/100mbps ethernet chip de conmutación

- Número de pieza.:

- KSZ8863RLL

- Fabricante:

- Microchip Technology

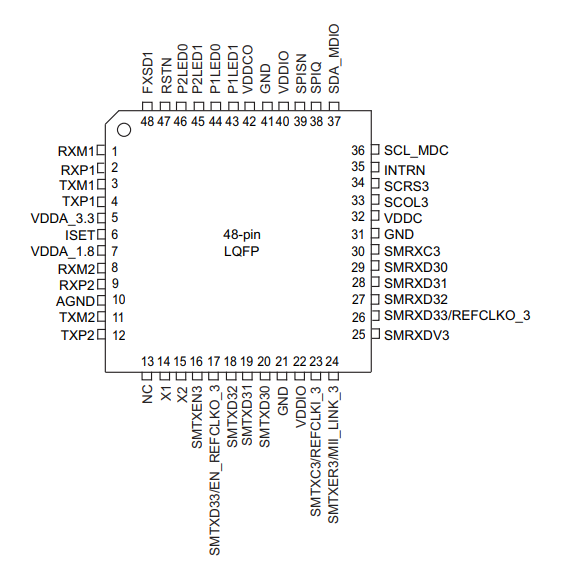

- Paquete:

- 48-LQFP

- Descripción:

- IC ETHERNET SW 3PORT 48-LQFP

- Quantity:

- Pago:

- Buques:

Detalles del artículo

- Detalles

- Especificaciones

- Comparación

El KSZ8863RLL es un conmutador de tres puertos de Microchip Technology con el tamaño de paquete más pequeño de la industria, diseñado para la nueva generación de sistemas de conmutación ethernet de 10/100 MBPS con número de puertos tierra, sensibilidad de costos y alta eficiencia energética. Ideal para aplicaciones en IPTV, decodificadores IP (ip-stb), VoIP, electrónica automotriz, así como en áreas industriales.

Notas: los tres puertos se definen generalmente como:

Puerto 1, puerto 2: puerto ethernet externo (RJ45 / optical port)

Forma del paquete: paquete sin plomo de 48 pines LQFP

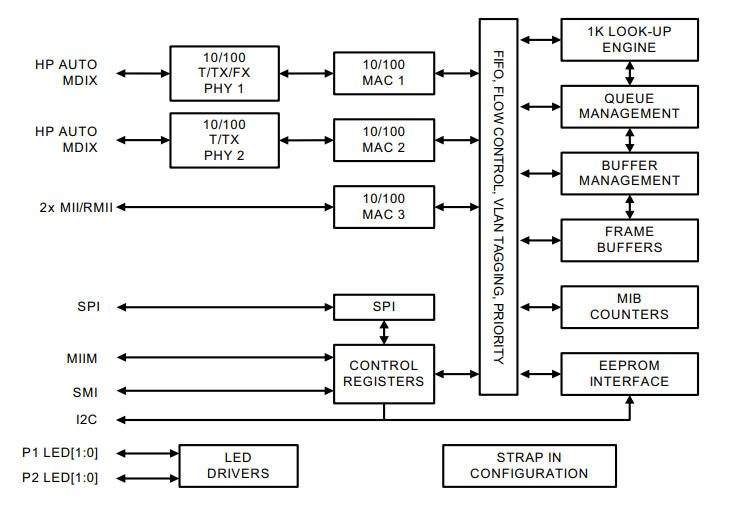

1. Principio arquitectónico integral

KSZ8863 integración interna:

Después de que el marco de datos de ethernet entre en el chip de intercambio, los pasos KSZ8863 procesan:

No es necesario. KSZ8863RLL integra 2 10/100 Mbps PHY internamente, solo necesita un transformador externo y un puerto RJ45

Q2: ¿Si KSZ8863RLL debe conectar MCU para trabajar?

No es necesario. KSZ8863RLL admite el modo no gestionado (no gestionado), que puede ejecutarse a través de enlace de pin o EEPROM; En modo Bypass, los datos se intercambian normalmente entre el puerto 1 y el puerto 2 incluso si la MCU está dormida o apagada.

Q3: ¿Cuál es el paquete y el requisito de la fuente de alimentación para KSZ8863RLL?

Notas: los tres puertos se definen generalmente como:

Puerto 1, puerto 2: puerto ethernet externo (RJ45 / optical port)

Puerto 3: conecte el procesador principal (MII/RMII)

Conoce a KSZ8863RLL

Key Features

Funciones avanzadas de intercambio

- Soporte IEEE 802.1q VLAN (hasta 16 grupos, VLAN ID completa), VLAN marking/demarking e inserción y eliminación de la etiqueta 802.1p/ Q, todos configurables por puerto

- Soporta limitación de velocidad de entrada/salida a nivel de puerto, supresión de tormentas de difusión (control de porcentaje global o a nivel de puerto) y protocolo IEEE 802.1d rapid span tree (RSTP)

- Soporta el modo Tail Tag para indicar al procesador el puerto de entrada del paquete y la prioridad

- Soporta el modo Bypass (Bypass), mantiene automáticamente el intercambio normal entre el puerto 1 y el puerto 2 cuando la CPU está dormida

- Apoye la filtración de la dirección MAC, su propia filtración de la dirección, apoye la dirección MAC independiente en el puerto 1/2

- Soporte IGMP Snooping (IPv4) multicast filtrado y QoS IPv4 / IPv6

- Soporta múltiples interfaces de gestión como SMI, MIIM, SPI, I²C para acceder al registro interno

- Soporte de enlace de pines de e/s y configuración EEPROM, para el modo de conmutación de tipo no gestionado

- Soporta configuración dinámica de registros (priorización de puertos, 802.1p/d/q, autonegociación, etc.)

- Soporta interfaz RMII y proporciona una salida de reloj de referencia de 50 MHz

- Soporte para priorización de paquetes por puerto, basado en 802.1p con DiffServ

- Soporta reasignación de prioridad a nivel de puerto 802.1p, proporciona colas de prioridad de 4 niveles

- Conmutador de 3 puertos 10/100 Mbps de tercera generación, integrado con 3 MAC + 2 PHY, compatible con IEEE 802.3u

- Arquitectura de conmutación sin bloqueo con tabla de direcciones MAC 1K + mecanismo de almacenamiento y reenvío

- Soporta full duplex IEEE 802.3x fluidising (PAUSE) con half duplex contrapresión fluidising

- Soporte de diagnóstico de cable Auto mdi-x y LinkMD®

- Apoye el modo MAC/PHY de la interfaz de MII y proporcione la indicación de estado completa del LED

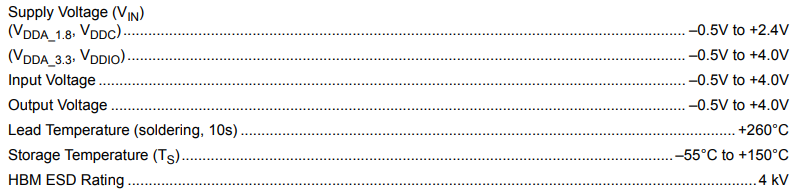

- HBM ESD grado de protección: 4 kV

- Soporte de imagen de puerto (entrada/salida) a cualquier puerto o interfaz MII

- Proporciona 34 MIB contadores estadísticos por puerto

- Admite el modo loopback para facilitar el diagnóstico remoto de fallas

- Soporte de pérdida de energía de todo el chip, ahorro de energía PHY a nivel de puerto, modo de detección de energía

- Soporta el apagado dinámico del árbol del reloj, reduce el consumo de energía total del sistema

- Fuente de alimentación única de 3.3v con 1.8v LDO integrado internamente

- VDDIO 3.3v / 2.5v / 1.8v opcional, fuente de alimentación del transceptor vdda_3.3 = 3.3v

Forma del paquete: paquete sin plomo de 48 pines LQFP

Diferencia entre KSZ8863RLL y KSZ8863MLL, KSZ8863FLL

Las principales diferencias son la interfaz de la CPU y la configuración del puerto:- KSZ8863MLL: dos transceptores 10/100base-t /TX + una interfaz MII

- KSZ8863RLL: dos transceptores 10/100base-t /TX + una interfaz RMII

- KSZ8863FLL: un 100base-fx, un 10/100base-t /TX transceptor + una interfaz MII

Pin de configuración

Valor nominal máximo absoluto

Usado por KSZ8863RLL

Con bajo consumo de energía, gestión de energía avanzada, así como una función de QoS perfecta, KSZ8863 está diseñado para cumplir con los requisitos verdes del sistema de conmutación de hoy. Además, el modo Bypass está disponible para lograr ahorros de energía a nivel del sistema.Principio de trabajo

KSZ8863 trabaja según el flujo del establecimiento del vínculo -- recepción de datos -- aprendizaje y juicio de la dirección -- transferencia inteligente del intercambio -- procesamiento de la exportación -- funcionamiento cooperativo o del bypass de la CPU -- ahorro de energía y supervisión1. Principio arquitectónico integral

KSZ8863 integración interna:

- Tres macs con ethernet

- 2 PHY de 10/100 Mbps

- Matriz de conmutación de alta velocidad (Switch Fabric)

- Tabla de búsqueda de direcciones (1K tabla MAC)

- QoS, VLAN y módulo de gestión de flujo

- Unidad de gestión y diagnóstico de energía

Después de que el marco de datos de ethernet entre en el chip de intercambio, los pasos KSZ8863 procesan:

- PHY recibe datos: el PHY del puerto 1/2 recibe la señal ethernet del cable de red o de la fibra y completa automáticamente la auto-negociación, detección de la tasa de identificación dúplex

- Desempaquetamiento y caché de MAC: el MAC recibe el marco de datos por completo, inspecciona el FCS y desecha el marco de error

- Aprendizaje de la dirección y tabla de búsqueda: intercambio de chips para aprender la dirección MAC de la fuente y escribir en la tabla MAC, de acuerdo con la consulta de la dirección MAC de destino a la publicación para determinar el puerto de reenvío

- Reenvío de matriz de conmutación: reenvío de paquetes al puerto de destino a través de una estructura de conmutación sin bloqueo

- Procesamiento de exportación: inserción/eliminación de la etiqueta VLAN según la configuración, ejecución de la programación de prioridad QoS, límite de velocidad, control de flujo

- Principio de VLAN: soporta IEEE 802.1q VLAN, los paquetes se aíslan o pasan de acuerdo con el puerto, la identificación de VLAN y las reglas de etiqueta

- Principio de QoS: la clasificación se basa en los campos 802.1p/DiffServ/IPv4 / IPv6, los marcos de datos se asignan a 4 prioridades y los datos de alta prioridad se reenvían con prioridad.

- Interfaz de la CPU: puerto 3 conectado con el procesador principal a través de MII o RMII, el procesador puede participar en la transmisión y recepción de datos o para la configuración y la gestión

- Modo Bypass: el chip de conmutación mantiene automáticamente el acceso de conmutación en los puertos 1 y 2 cuando el procesador entra en estado de hibernización o pérdida de energía, sin tener que confiar en la CPU, lo que garantiza que la comunicación de red no sea interrumpida y logra un bajo consumo de energía a nivel del sistema

- El chip inserta una identificación de 1 byte delante del marco de datos FCS (puerto de entrada del paquete, información de prioridad)

- Cuando el procesador recibe datos a través del puerto 3, puede determinar rápidamente el origen y la prioridad de los datos

- Ideal para simplificar el procesamiento de la pila de protocolos en el lado de la CPU

- Modo full duplex: control de flujo con el marco IEEE 802.3x PAUSE

- Modo half duplex: mecanismo de contrapresión para evitar conflictos de datos

- Auto mdi-x: identificación automática de líneas de paso/líneas cruzadas

- LinkMD® : detección de fallos tales como rotura de cable de red y cortocircuito a través del principio TDR

- Pérdida de energía de todo el software del chip: apague el módulo principal

- Ahorro de energía PHY a nivel de puerto: apague el transceptor cuando el enlace esté inactivo

- Modo de detección de energía: hibernación automática sin señal

- Cierre dinámico del reloj: sólo la lógica necesaria se mantiene funcionando

La aplicación

- Telefonía por internet

- Set top box/consola de juegos industria automotriz

- Controles industriales

- IPTV tipo de concentración distribución de fibra

- Pequeña oficina oficina en casa puerta de enlace residencial

- Desconexión de banda ancha/firewall/red privada virtual

- Línea de abonado digital integrada/módem por cable

- Punto de acceso wlan + gateway

- Interruptor independiente 10/100

Preguntas frecuentes sobre KSZ8863RLL

Q1: ¿Necesita un PHY externo para KSZ8863RLL?No es necesario. KSZ8863RLL integra 2 10/100 Mbps PHY internamente, solo necesita un transformador externo y un puerto RJ45

Q2: ¿Si KSZ8863RLL debe conectar MCU para trabajar?

No es necesario. KSZ8863RLL admite el modo no gestionado (no gestionado), que puede ejecutarse a través de enlace de pin o EEPROM; En modo Bypass, los datos se intercambian normalmente entre el puerto 1 y el puerto 2 incluso si la MCU está dormida o apagada.

Q3: ¿Cuál es el paquete y el requisito de la fuente de alimentación para KSZ8863RLL?

- Paquete: 48-pin LQFP (sin plomo, RoHS)

- Fuente de alimentación del núcleo: 3.3v

- VDDIO: ayuda 3.3v / 2.5v / 1.8v

- 1.8v LDO integrado internamente

- Atributos del producto

- Valor del atributo

- Fabricante:

- Microchip Technology

- Serie:

- -

- Paquete/Caja:

- 48-LQFP

- Embalaje:

- Tray

- Estado del producto:

- Active

- Resistencia:

- Not Verified

- Tolerancia:

- Ethernet

- Potencia (vatios):

- Switch

- Composición:

- I2C, SPI

- Características:

- 10/100 Base-T/TX PHY

- Coeficiente de temperatura:

- 1.8V, 2.5V, 3.3V

- Temperatura de funcionamiento:

- -

- Proveedor Dispositivo Paquete:

- 0°C ~ 70°C

- Clasificaciones:

- 48-LQFP (7x7)

- Tamaño/Dimensión:

- -

- Altura - Asentado (Máx.):

- -

- Número de terminaciones:

- Tasa de fallos:

| Imagen |

| Número de pieza |

| Fabricante |

| Paquete/Caja |

| Programable |

| Protocolo |

| Función |

| Interfaz |

| Estándares |

| Voltaje - Suministro |

| Corriente - Suministro |

| Temperatura de funcionamiento |

| Proveedor Dispositivo Paquete |

| Grado |

| Calificación |

Inventario:3,736

Por favor, envíe una consulta.Por favor, envíenos su pregunta y responderemos de inmediato.

-

PTN5150AHXMP

NXP USA Inc.

-

USB3740B-AI9-TR

Microchip Technology

-

USB3740B-AI2-TR

Microchip Technology

-

USB3300-EZK-TR

Microchip Technology

-

USB3300-EZK

Microchip Technology

-

FUSB340TMX

onsemi