Atrapar el ciclo de aumento de precio de los chips de almacenamiento: una comprensión profunda del rendimiento del mercado y el valor de W25Q16JVSSIQ

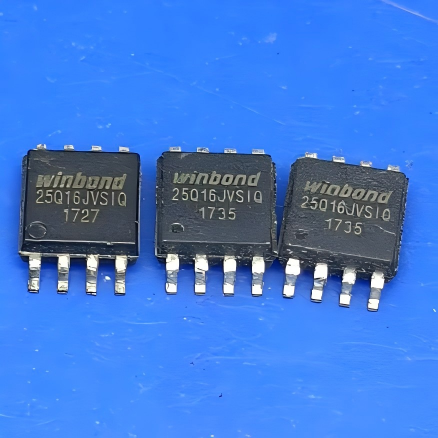

- Número de pieza.:

- W25Q16JVSSIQ

- Fabricante:

- Winbond Electronics Corporation

- Paquete:

- 8-SOIC (0.209", 5.30mm Width)

- Descripción:

- IC FLASH 16MBIT SPI/QUAD 8SOIC

- Quantity:

- Pago:

- Buques:

Detalles del artículo

- Detalles

- Especificaciones

- Comparación

Conoce a W25Q16JVSSIQ

W25Q16JVSSIQ es un chip de memoria Flash NOR Serial de 16 Mbit de Winbond con interfaz de e/s SPI/Quad, soporta hasta aproximadamente 133 MHz de frecuencia de reloj y 2.7v ~ 3.6v de voltaje de alimentación, Ideal para sistemas embebidos para almacenar firmware, datos y configuraciones.

Características/características

- Nueva serie de memorias flash SPI

- W25Q16JV: 16M bits / 2M bytes (2.097.152)

- SPI estándar: reloj (CLK), selección de piezas (/CS), entrada de datos (DI), salida de datos (DO)

- doble SPI: reloj (CLK), selección de piezas (/CS), IO0, IO1

- SPI cuádruple: reloj (CLK), selección de piezas (/CS), IO0, IO1, IO2, IO3

- restablecimiento de software y hardware (1)

- Más alto rendimiento serial flash

- frecuencia de reloj SPI única 133MHz, doble/cuádruple frecuencia de reloj SPI 266/532mhz

- tasa de transferencia de datos continua de 66MB/S

- mínimo 100K ciclos de programa/borrado por sector

- retención de datos de más de 20 años

- Eficiente "lectura continua"

- con 8/16/32/64 bytes de lectura cíclica

- mínimo de 8 ciclos de reloj para acceder a la memoria

- permite la verdadera operación XIP (ejecución de bits)

- mejor rendimiento que la memoria flash paralela X16

- Bajo consumo de energía y amplio rango de temperatura

- rango de voltaje de alimentación única de 2.7v a 3.6v

- rango de temperatura de funcionamiento de -40°C a +85°C

- rango de temperatura de funcionamiento de -40°C a +105°C

- consumo de energía <1µA en modo de reposo (típico)

- Arquitectura flexible, sector 4KB

- sector unificado/borrado de bloque (4K/32K/64K bytes)

- programable de 1 a 256 bytes por página programable

- borrado/programación pausa y reanudación

- Características de seguridad avanzadas

- protección contra escritura de software y hardware

- bloqueo de energía

- protección especial OTP (2)

- identificador único de 64 bits para cada dispositivo - registro de parámetros detectables (SFDP)

- registro de seguridad de 3X256 bytes con un mecanismo de bloqueo programado de una sola vez

- almacenamiento temporal vs bits de registro de estado de almacenamiento no temporal

- Encapsulación eficiente del espacio

- 8 pines SOIC (150 micrones /208 micrones)

- 8 pines USON (2X3 mm /4X3 mm)

- 8 pines XSON (4X4 mm)

- 8 pines WSON (6X5 mm)

- 8 bolas WLCSP

- póngase en contacto con wangbang para KGD y otras opciones

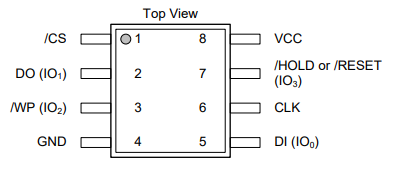

Configuración de pin

1 :/CS-- I --Chip Select Input

2:DO (IO1) --I/O --Data Output (Data Input Output 1)

3:/WP (IO2)-- I/O --Write Protect Input ( Data Input Output 2)

4: GND-- Ground

5: DI (IO0)-- I/O --Data Input (Data Input Output 0)

6 :CLK-- I-- Serial Clock Input

7:/HOLD or /RESET(IO3) --I/O-- Hold or Reset Input (Data Input Output 3)

8: VCC-- Power Supply

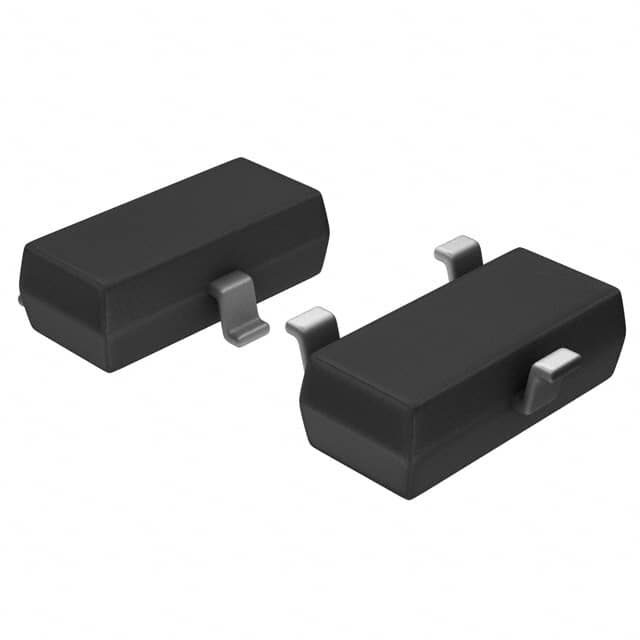

Valor nominal máximo absoluto

Uso de W25Q16JVSSIQ

Explicación del principio de funcionamiento

W25Q16JVSSIQ se comunica con el control principal a través de la interfaz SPI/Quad SPI. Con la estructura de almacenamiento NOR Flash, el W25Q16JVSSIQ realiza la lectura aleatoria, la escritura y el borrado del código del programa y de los datos sin pérdida de datos sin pérdida de energía.1. Principio de la estructura de almacenamiento interno: W25Q16JVSSIQ pertenece a ni Flash, la lectura se puede acceder directamente por dirección, la escritura y el borrado deben realizar la operación de borrado primero.

2. Flujo de trabajo de comunicación SPI: selección de chip -- entrada de instrucciones -- fase de dirección -- transmisión de datos -- detección de estado

3. Mecanismo de trabajo de lectura/escritura/borrado

- Lectura: no hay necesidad de borrar, soporte estándar SPI/Dual/Quad SPI, se puede utilizar directamente para el almacenamiento del programa con la ejecución XIP

- Escritura: Write Enable debe ejecutarse primero, solo puede escribir bit de 1 a 0

- Borrado: restaurar la unidad de almacenamiento a un estado completo 1 con una unidad de borrado más grande

Application

- Almacenamiento de código de arranque MCU

- Actualización de firmware (OTA)

- Configuración de parámetros

- Registro de datos guardados

Realización del valor de W25Q16JVSSIQ en un ciclo de aumento de precios

Bajo el ambiente general de aumento de precios en el mercado, W25Q16JVSSIQ tiene varios puntos competitivos- Estabilidad fuerte: como la serie de productos maduros de Winbond, tiene suministro estable con capacidad de producción en masa;

- Ventajas de costo obviosas: comparado con los productos de gran capacidad NAND y DRAM, su costo por unidad de capacidad y el costo total todavía son más bajos;

- Adaptación amplia: en el embedded, IoT, automotriz, control industrial y otros campos todavía se mantienen los requisitos de aplicación principales;

- Elasticidad de la estrategia de inventario: capacidad de amortiguar el riesgo de volatilidad de precios a corto plazo a través de la producción en masa con control de inventario.

La tendencia actual del mercado para W25Q16JVSSIQ este tipo de chip de memoria

Wanghong, un fabricante chino taiwanés, señaló que la demanda en el mercado de computadoras y servidores se había recuperado antes y que los precios de los NOR al consumidor se habían recuperado. Otros fabricantes ya en octubre de 2025 dijeron que los productos de pequeña y mediana capacidad NOR Flash también estaban experimentando una tendencia al alza de precios. La capacidad total de NOR Flash está enlazada. Entre ellos, los productos de gran capacidad tienen un alto valor individual y un gran consumo de capacidad. En el momento de la escasez de suministro, los productos de gran capacidad experimentarán un aumento de precio temprano y gradualmente se trasladarán a los productos de pequeña y mediana capacidad. Se espera que NOR Flash durante todo el año 2026 todavía mantenga el ritmo general de aumento moderado de precios.Los analistas de moore señalan que el aumento de 30 a 100 por ciento en el precio de la transmisión de NOR Flash se debe a "los resultados de la eliminación de la cadena de suministro". El actual gasto de capital mundial en semiconductores está inundando productos clave de servidores AI como HBM (memoria de alto ancho de banda) y DDR5, debido a su excelente rentabilidad bruta, que absorbe demasiado dinero y capacidad. Sin embargo, aunque el proceso de orden más alto no es requerido, la demanda del mercado no ha desaparecido, lo que ha dado lugar a una grave brecha estructural en la línea de productos maduros. Destacó que, aunque DRAM, NAND y NOR Flash no son los productos de primera línea, el actual aumento de precios es precisamente el resultado de una "falta de configuración de capacidad". El mercado de almacenamiento estará dominado hoy por el precio "quien paga más recibe".

Asesoramiento en estrategia de cadena de suministro

- Suministro de bloqueo por adelantado: para W25Q16JVSSIQ y otros dispositivos comunes, contrato y compra por adelantado, reducir el riesgo de subida de precios;

- Estrategia de regulación de inventario: establecer un inventario de seguridad razonable para hacer frente a las fluctuaciones cíclicas de precios;

- Atributos del producto

- Valor del atributo

- Fabricante:

- Winbond Electronics Corporation

- Serie:

- SpiFlash®

- Paquete/Caja:

- 8-SOIC (0.209", 5.30mm Width)

- Embalaje:

- Tube

- Estado del producto:

- Active

- Resistencia:

- Verified

- Tolerancia:

- Non-Volatile

- Potencia (vatios):

- FLASH

- Composición:

- FLASH - NOR

- Características:

- 16Mbit

- Coeficiente de temperatura:

- 2M x 8

- Temperatura de funcionamiento:

- SPI - Quad I/O

- Proveedor Dispositivo Paquete:

- 133 MHz

- Clasificaciones:

- 3ms

- Tamaño/Dimensión:

- -

- Altura - Asentado (Máx.):

- 2.7V ~ 3.6V

- Número de terminaciones:

- -40°C ~ 85°C (TA)

- Tasa de fallos:

- -

| Imagen |

| Número de pieza |

| Fabricante |

| Serie |

| Paquete/Caja |

| Embalaje |

| Estado del producto |

| Programable |

| Tipo de memoria |

| Formato de memoria |

| Tecnología |

| Tamaño de la memoria |

| Organización de la memoria |

| Interfaz de memoria |

| Frecuencia de reloj |

| Tiempo de ciclo de escritura - Palabra, página |

| Tiempo de acceso |

| Voltaje - Suministro |

| Temperatura de funcionamiento |

| Grado |

| Calificación |

| Tipo de montaje |

| Proveedor Dispositivo Paquete |

Inventario:235,483

Por favor, envíe una consulta.Por favor, envíenos su pregunta y responderemos de inmediato.

-

M24C02-WMN6TP

STMicroelectronics

-

AT24C02C-XHM-T

Microchip Technology

-

AT21CS01-STUM10-T

Microchip Technology

-

AT24C02C-SSHM-T

Microchip Technology

-

24LC01BT-I/OT

Microchip Technology

-

M24C02-FMC6TG

STMicroelectronics